Increasing security in heterogeneous IC packages

Background

As the semiconductor and integrated circuit (IC) industry continues to globalize and specialize, more vendors are becoming involved with the fabrication and packaging of each IC. While this brings benefit of improved chip performance and new functionalities, it also creates opportunity for chip tampering and counterfeiting.

To address this growing concerns of chip and intellectual property security, our group is working in collaboration with Dr. Navid Asadi in UF’s Electrical and Computing Engineering department to design, prototype, and test novel packaging architectures with improved security.

Project Description

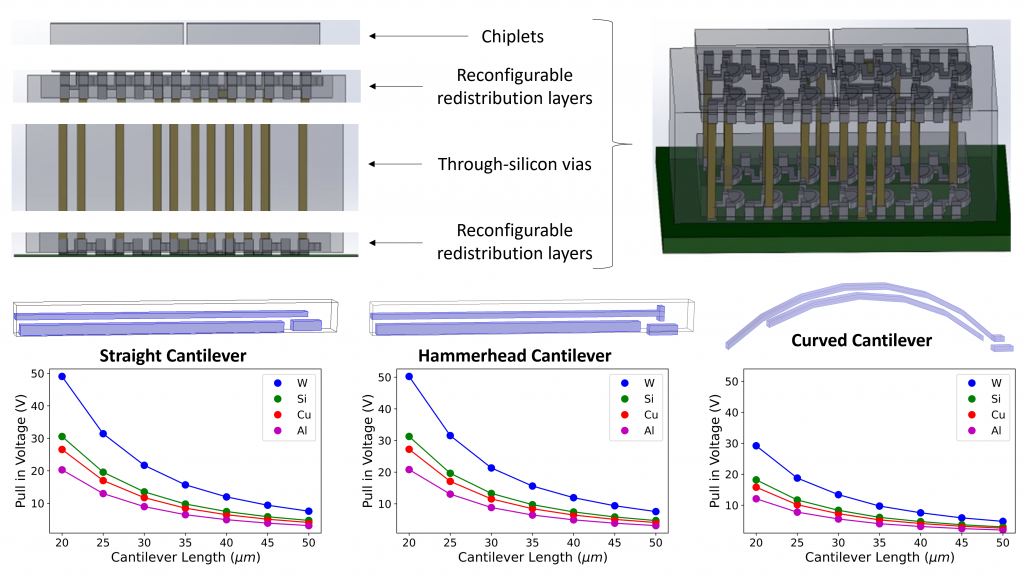

As a first step in this direction, we have designed a generic silicon interposer (carrier wafer) in which the chiplet-to-chiplet interconnect network is obfuscated through an array of bi-directional micro-electrical-mechanical switches (MEMS).

This work is supported by the Semiconductor Research Corporation under Award No. 2021-HW-3063.